集成電路CAD設計中的核心環節 芯片焊盤與版圖布局研發探析

在當今高速發展的半導體產業中,集成電路(IC)的計算機輔助設計(CAD)扮演著至關重要的角色。其中,芯片焊盤(Pad)設計與版圖(Layout)布局設計不僅是連接芯片內部電路與外部世界的物理橋梁,更是決定芯片性能、可靠性及制造成本的關鍵研發環節。本文旨在深入探討這兩大核心設計領域的研發要點與技術趨勢。

芯片焊盤設計:性能與可靠性的門戶

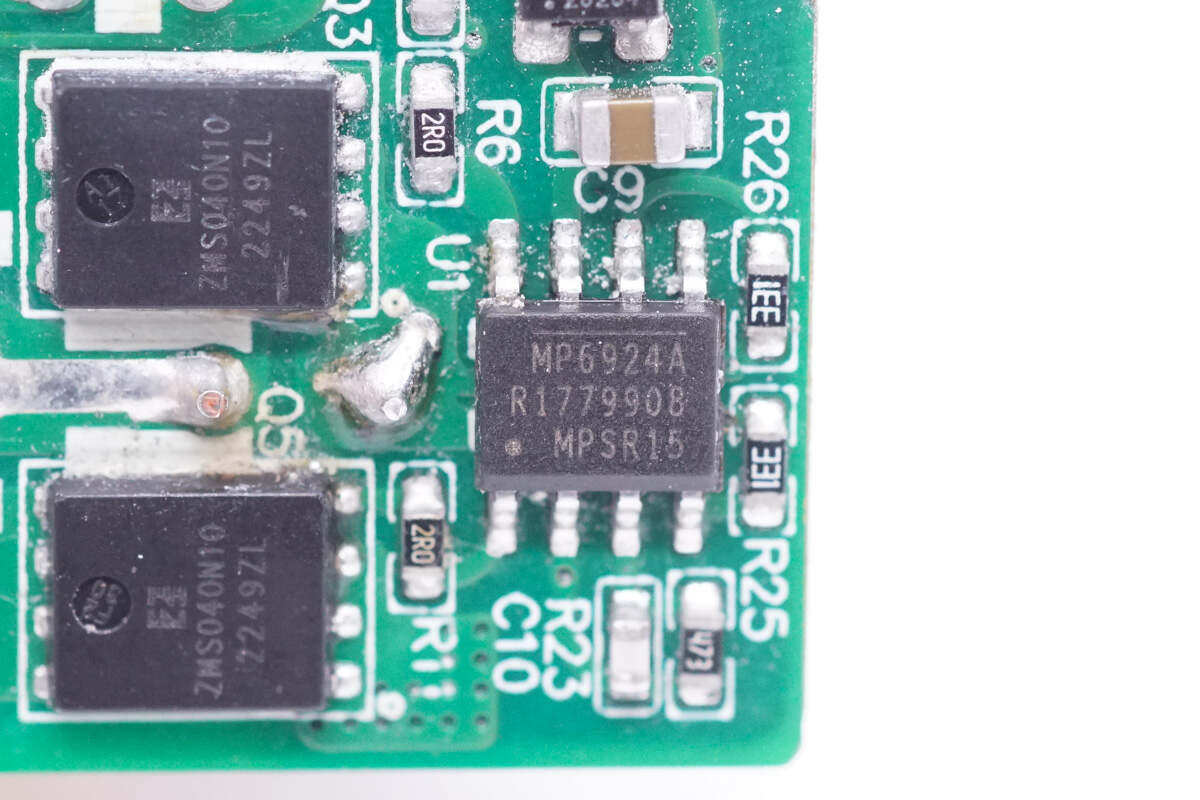

芯片焊盤,作為芯片與封裝基板或直接與印制電路板(PCB)進行電氣連接和機械固定的金屬區域,其設計直接影響到信號的完整性、電源的穩定性以及芯片的長期可靠性。

1. 設計考量與挑戰:

- 電氣特性:焊盤的尺寸、形狀和間距需精確計算,以匹配傳輸線的阻抗,減少信號反射與損耗,尤其是在高頻、高速應用中。電源和接地焊盤需要足夠大的面積和低阻抗路徑,以確保穩定的電壓供應和有效的噪聲泄放。

- 機械與熱可靠性:焊盤必須能夠承受封裝過程中的鍵合(如引線鍵合、倒裝芯片凸點)應力,以及產品生命周期中的熱循環應力。材料選擇、焊盤下方的金屬堆疊結構(Under Bump Metallization, UBM)設計都至關重要。

- 可制造性設計(DFM):設計需嚴格遵循晶圓廠和封裝廠的設計規則(Design Rule),確保光刻、刻蝕、電鍍等工藝的可行性,避免短路、斷路等缺陷。

2. 研發趨勢:

- 隨著芯片向多芯片模塊(MCM)、系統級封裝(SiP)和2.5D/3D集成發展,焊盤設計變得更加復雜,需要支持更細間距的微凸點(Micro-bump)和硅通孔(TSV)技術。

- 針對先進工藝節點(如7nm、5nm及以下),焊盤設計需與前端設計(FEOL)協同優化,以應對更嚴格的電遷移(Electromigration)和自熱效應挑戰。

版圖布局設計:性能、功耗與面積的精妙平衡

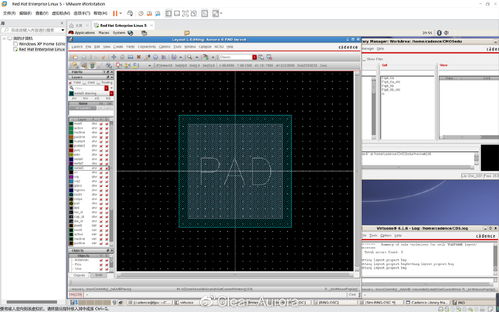

版圖布局是將電路網表(Netlist)轉化為一系列幾何圖形(多邊形)的過程,這些圖形定義了芯片上每一層材料的形狀,是集成電路物理實現的藍圖。

1. 設計核心任務:

- 物理實現:根據邏輯綜合后的網表,進行布局(Placement)、布線(Routing)和物理驗證(Physical Verification)。布局決定了每個標準單元、宏模塊(如存儲器、模擬模塊)在芯片上的位置,目標是優化時序、降低互連線延遲和功耗。

- 信號完整性管理:在高密度設計中,串擾(Crosstalk)、電源網絡噪聲(IR Drop、電源地反彈)等問題突出。研發重點在于通過合理的電源網格設計、時鐘樹綜合(CTS)和屏蔽布線等技術來保障信號純凈度。

- 設計規則與工藝兼容性:必須嚴格遵守復雜的幾何設計規則(DRC)、電氣規則(ERC)以及針對可制造性的規則(如光學鄰近效應修正OPC、多重圖形化要求)。

2. 研發方法與工具演進:

- 自動化與智能化:傳統的全定制(Full-custom)和半定制(Semi-custom)設計方法正與高度自動化的數字設計流程(RTL-to-GDSII)深度融合。機器學習(ML)和人工智能(AI)技術開始應用于布局預測、熱點檢測和設計空間探索,以加速迭代并優化PPA(性能、功耗、面積)。

- 系統級協同設計:版圖設計不再孤立,需要與系統架構、封裝設計(Co-design)乃至散熱分析進行早期協同。對于模擬/射頻電路和高速數字接口,版圖的物理效應(寄生參數)必須在前端設計階段就被充分考慮。

- 應對先進工藝:在FinFET、GAA等晶體管結構下,版圖設計需處理三維效應、更復雜的器件模型和更苛刻的可靠性約束(如自熱、NBTI等)。

面向未來的研發融合

芯片焊盤設計與版圖布局設計是集成電路CAD研發中密不可分的兩部分。焊盤是芯片對外的“接口標準”,而版圖則是其內部的“城市規劃和交通網絡”。未來的研發方向將更加注重:

- 前后端與封裝的協同優化:從系統級出發,實現芯片-封裝-板級的統一設計和優化。

- EDA工具的持續創新:開發更智能、更高效的CAD工具,以管理日益增長的設計復雜度和數據量。

- 新材料與新工藝的快速適配:針對碳納米管、二維材料等新興半導體技術,以及新型封裝形式,迅速建立相應的設計方法和規則。

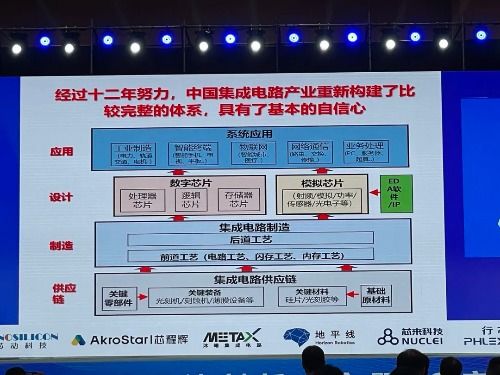

在摩爾定律持續推進與超越摩爾定律(More than Moore)并行的時代,對芯片焊盤及版圖布局設計的深入研發,是保障我國集成電路產業自主創新與核心競爭力提升的關鍵技術基石。工程師們需要在嚴謹的物理約束與創造性的設計優化之間不斷探索,方能鑄造出性能卓越、穩定可靠的芯片產品。

如若轉載,請注明出處:http://www.a6a4.cn/product/57.html

更新時間:2026-01-19 20:46:56