集成電路CAD課程實(shí)驗(yàn)報(bào)告 二輸入與非門(mén)電路設(shè)計(jì)與版圖仿真

一、 實(shí)驗(yàn)?zāi)康?/strong>

本實(shí)驗(yàn)旨在通過(guò)使用集成電路計(jì)算機(jī)輔助設(shè)計(jì)工具,完成一個(gè)標(biāo)準(zhǔn)CMOS二輸入與非門(mén)(NAND2)的全流程設(shè)計(jì),包括電路圖設(shè)計(jì)、邏輯功能驗(yàn)證、版圖設(shè)計(jì)與物理驗(yàn)證,以及后仿真分析。通過(guò)本實(shí)驗(yàn),深入理解CMOS數(shù)字集成電路的基本單元結(jié)構(gòu)、設(shè)計(jì)方法、版圖設(shè)計(jì)規(guī)則以及從電路到版圖的實(shí)現(xiàn)過(guò)程。

二、 實(shí)驗(yàn)內(nèi)容

- 電路設(shè)計(jì)與前仿真: 在電路圖編輯環(huán)境中,搭建CMOS二輸入與非門(mén)電路,進(jìn)行直流分析、瞬態(tài)分析,驗(yàn)證其邏輯功能(00→1, 01→1, 10→1, 11→0)和關(guān)鍵電學(xué)特性(如傳輸延遲、功耗)。

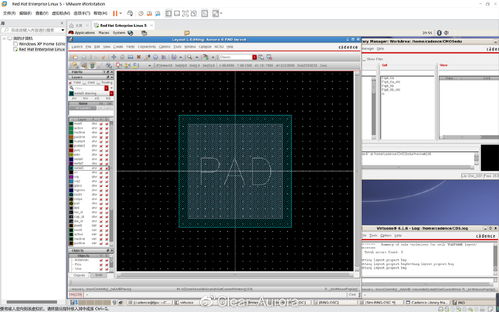

- 版圖設(shè)計(jì): 根據(jù)給定的設(shè)計(jì)規(guī)則(DRC),在版圖編輯器中繪制二輸入與非門(mén)的物理版圖。版圖需包含兩個(gè)串聯(lián)的PMOS管和兩個(gè)并聯(lián)的NMOS管,以及VDD、GND、輸入A/B和輸出Y的金屬連接。

- 物理驗(yàn)證: 對(duì)完成的版圖進(jìn)行設(shè)計(jì)規(guī)則檢查(DRC)和電路與版圖一致性檢查(LVS),確保版圖符合工藝要求且與原始電路圖在電學(xué)上等效。

- 寄生參數(shù)提取與后仿真: 從驗(yàn)證通過(guò)的版圖中提取寄生電阻和電容(RC提取),生成包含寄生效應(yīng)的仿真網(wǎng)表,并進(jìn)行后仿真。對(duì)比前仿與后仿結(jié)果,分析寄生效應(yīng)(如連線延遲)對(duì)電路性能的影響。

三、 實(shí)驗(yàn)原理

CMOS二輸入與非門(mén)的布爾表達(dá)式為:Y = /(A·B)。其電路結(jié)構(gòu)由兩部分組成:

- 上拉網(wǎng)絡(luò)(PUN): 由兩個(gè)PMOS管并聯(lián)構(gòu)成。當(dāng)A和B均為高電平時(shí),兩個(gè)PMOS管均關(guān)閉;其他任何輸入組合下,至少有一個(gè)PMOS管導(dǎo)通,將輸出Y上拉至VDD(邏輯1)。

- 下拉網(wǎng)絡(luò)(PDN): 由兩個(gè)NMOS管串聯(lián)構(gòu)成。僅當(dāng)A和B均為高電平時(shí),兩個(gè)NMOS管同時(shí)導(dǎo)通,將輸出Y下拉至GND(邏輯0)。

版圖設(shè)計(jì)是將這種晶體管級(jí)的電路連接關(guān)系,轉(zhuǎn)化為符合特定集成電路制造工藝幾何規(guī)則和電學(xué)規(guī)則的物理掩模圖形。設(shè)計(jì)時(shí)需遵循最小線寬、最小間距、阱和襯底接觸等規(guī)則,并考慮器件匹配、連線優(yōu)化以減少寄生效應(yīng)。

四、 實(shí)驗(yàn)步驟與結(jié)果分析

- 電路圖設(shè)計(jì)與前仿真:

- 使用Cadence Virtuoso Schematic Editor搭建電路。PMOS和NMOS的寬長(zhǎng)比(W/L)根據(jù)驅(qū)動(dòng)能力和速度要求進(jìn)行初步設(shè)定(例如,PMOS W/L設(shè)置為NMOS的2-2.5倍以補(bǔ)償空穴遷移率較低的問(wèn)題)。

- 使用Spectre仿真器進(jìn)行瞬態(tài)分析。輸入A、B施加包含所有四種組合的脈沖信號(hào)。仿真波形清晰顯示輸出Y完全符合與非邏輯功能。測(cè)量得到(在典型工藝角下)輸出由高到低的傳輸延遲(tphl)和由低到高的傳輸延遲(tplh),并估算平均靜態(tài)功耗和動(dòng)態(tài)功耗。

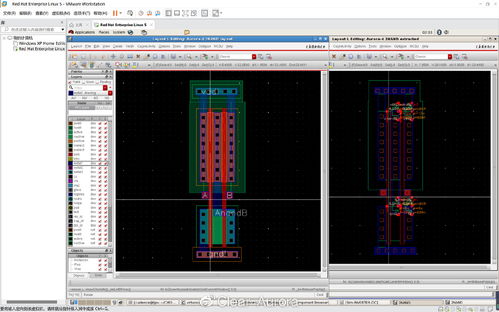

- 版圖設(shè)計(jì)與物理驗(yàn)證:

- 使用Virtuoso Layout Editor繪制版圖。關(guān)鍵步驟包括:

- 繪制N-well,并在其中布置兩個(gè)并聯(lián)的PMOS管,共享源極(接VDD)和N-well接觸。

- 在P-substrate上布置兩個(gè)串聯(lián)的NMOS管,共享源極(接GND)和襯底接觸。

- 使用Poly硅柵連接兩個(gè)輸入信號(hào)A和B,確保PMOS和NMOS的柵極正確對(duì)齊。

- 使用Metal1完成晶體管源/漏極的內(nèi)部連接以及到電源、地和輸出節(jié)點(diǎn)的連接。

- 添加輸入/輸出端口(PIN)。

- 運(yùn)行DRC檢查,根據(jù)報(bào)錯(cuò)信息修改版圖,直至無(wú)任何違反設(shè)計(jì)規(guī)則的錯(cuò)誤。

- 運(yùn)行LVS檢查,提供網(wǎng)表對(duì)比。成功通過(guò)LVS,證明版圖與原理圖在晶體管類(lèi)型、數(shù)量及連接關(guān)系上完全一致。

- 寄生參數(shù)提取與后仿真:

- 對(duì)通過(guò)驗(yàn)證的版圖進(jìn)行RC提取(使用Quantus或類(lèi)似工具),生成包含所有寄生電阻和電容的詳細(xì)網(wǎng)表(SPICE格式)。

- 使用該網(wǎng)表進(jìn)行后仿真,施加與前仿真相同的測(cè)試向量。

- 結(jié)果對(duì)比分析: 后仿真波形顯示邏輯功能依然正確,但信號(hào)的邊沿變得略微平緩,傳輸延遲明顯增加。例如,tphl和tplh可能比前仿結(jié)果增大20%-50%,具體數(shù)值取決于工藝節(jié)點(diǎn)和版圖布線長(zhǎng)度。這是由于金屬連線和通孔的寄生電阻電容引入了額外的RC延遲。動(dòng)態(tài)功耗也可能因?qū)纳娙莩浞烹姸杂猩仙4私Y(jié)果凸顯了在深亞微米設(shè)計(jì)中,互連線延遲已成為制約電路性能的關(guān)鍵因素,版圖優(yōu)化(如縮短關(guān)鍵路徑連線、使用高層金屬等)至關(guān)重要。

五、 實(shí)驗(yàn)結(jié)論與研發(fā)意義

本次實(shí)驗(yàn)成功完成了CMOS二輸入與非門(mén)從電路設(shè)計(jì)到物理實(shí)現(xiàn)的完整流程。通過(guò)前仿真驗(yàn)證了邏輯功能的正確性,通過(guò)版圖設(shè)計(jì)實(shí)現(xiàn)了電路的物理描述,并通過(guò)DRC/LVS確保了其可制造性和電學(xué)等效性。通過(guò)后仿真定量分析了寄生參數(shù)對(duì)電路性能(主要是速度)的影響。

從研發(fā)角度而言,本實(shí)驗(yàn)所練習(xí)的全流程是現(xiàn)代數(shù)字集成電路芯片研發(fā)中標(biāo)準(zhǔn)單元庫(kù)開(kāi)發(fā)、定制電路模塊設(shè)計(jì)的基礎(chǔ)環(huán)節(jié)。掌握這一流程意味著:

- 理解了電路性能(速度、功耗、面積)與晶體管尺寸、版圖布局之間的內(nèi)在聯(lián)系,為后續(xù)電路優(yōu)化提供了依據(jù)。

- 熟悉了使用EDA工具進(jìn)行自動(dòng)化驗(yàn)證(DRC/LVS)和寄生提取的方法,這是保證芯片設(shè)計(jì)一次成功(First Silicon Success)的關(guān)鍵質(zhì)量保障步驟。

- 認(rèn)識(shí)到前端電路設(shè)計(jì)與后端物理實(shí)現(xiàn)必須協(xié)同考慮(設(shè)計(jì)協(xié)同),尤其是在高性能或低功耗設(shè)計(jì)中,需要迭代優(yōu)化以達(dá)到設(shè)計(jì)目標(biāo)。

因此,本實(shí)驗(yàn)不僅是學(xué)習(xí)工具使用的實(shí)踐課,更是通向?qū)嶋H集成電路研發(fā)工作的重要橋梁。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.a6a4.cn/product/41.html

更新時(shí)間:2026-01-19 15:55:28