模擬CMOS集成電路設(shè)計(jì) 拉扎維課件——從0到1掌握模擬電路研發(fā)

模擬CMOS集成電路設(shè)計(jì)是現(xiàn)代電子工程領(lǐng)域的核心技術(shù)之一,廣泛應(yīng)用于通信、醫(yī)療和消費(fèi)電子等行業(yè)。本文以Behzad Razavi的經(jīng)典課件為基礎(chǔ),為你系統(tǒng)介紹從基礎(chǔ)概念到實(shí)際設(shè)計(jì)的全過程,助你快速入門模擬電路研發(fā)。

一、模擬電路設(shè)計(jì)基礎(chǔ)

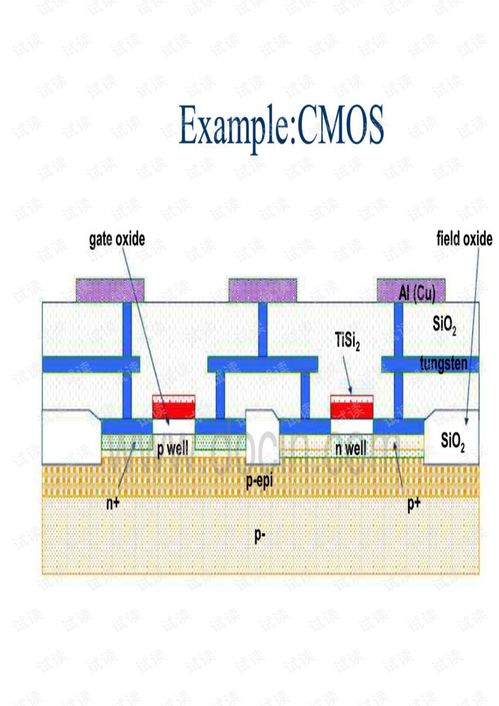

模擬電路處理連續(xù)信號(hào),與數(shù)字電路不同,它依賴于晶體管在飽和區(qū)的特性。CMOS技術(shù)因其低功耗和高集成度成為主流。拉扎維課件首先講解MOSFET的工作原理,包括閾值電壓、跨導(dǎo)和輸出電阻等關(guān)鍵參數(shù),為后續(xù)設(shè)計(jì)打下堅(jiān)實(shí)基礎(chǔ)。

二、關(guān)鍵模塊設(shè)計(jì)

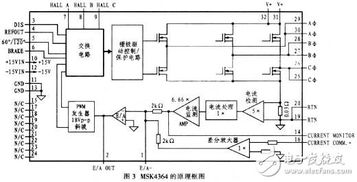

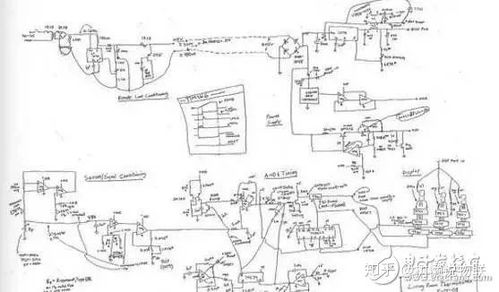

課件深入解析了模擬電路的核心模塊:放大器、電流鏡和偏置電路。例如,單級(jí)放大器(如共源放大器)的設(shè)計(jì)需要考慮增益、帶寬和穩(wěn)定性。拉扎維通過直觀的公式和實(shí)例,教你如何計(jì)算和優(yōu)化這些參數(shù),確保電路在真實(shí)環(huán)境中可靠工作。

三、從理論到實(shí)踐:設(shè)計(jì)流程

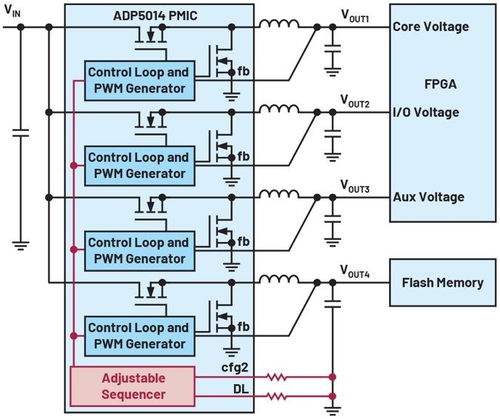

模擬電路設(shè)計(jì)遵循系統(tǒng)化的流程:從規(guī)格定義、電路拓?fù)溥x擇,到仿真和版圖設(shè)計(jì)。拉扎維課件強(qiáng)調(diào)使用SPICE工具進(jìn)行仿真,驗(yàn)證電路性能。他介紹了版圖設(shè)計(jì)的注意事項(xiàng),如匹配、噪聲抑制和寄生效應(yīng)處理,幫助你避免常見錯(cuò)誤。

四、常見挑戰(zhàn)與解決方案

在實(shí)際研發(fā)中,模擬電路常面臨噪聲、功耗和工藝變化等挑戰(zhàn)。課件提供了實(shí)用的解決策略,例如使用差分結(jié)構(gòu)減少噪聲,或通過自適應(yīng)偏置應(yīng)對(duì)工藝偏差。這些經(jīng)驗(yàn)源自工業(yè)實(shí)踐,能加速你的學(xué)習(xí)曲線。

五、總結(jié)與進(jìn)階建議

通過拉扎維課件,你可以建立完整的模擬CMOS設(shè)計(jì)知識(shí)框架。建議結(jié)合實(shí)驗(yàn)和項(xiàng)目實(shí)踐,逐步提升設(shè)計(jì)能力。記住,模擬電路設(shè)計(jì)既是科學(xué)也是藝術(shù),需要持續(xù)學(xué)習(xí)和迭代。從0到1的旅程雖具挑戰(zhàn),但掌握了這些核心概念,你就能在研發(fā)領(lǐng)域游刃有余。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.a6a4.cn/product/18.html

更新時(shí)間:2026-01-19 08:37:40